Mission of the DfX Lab:

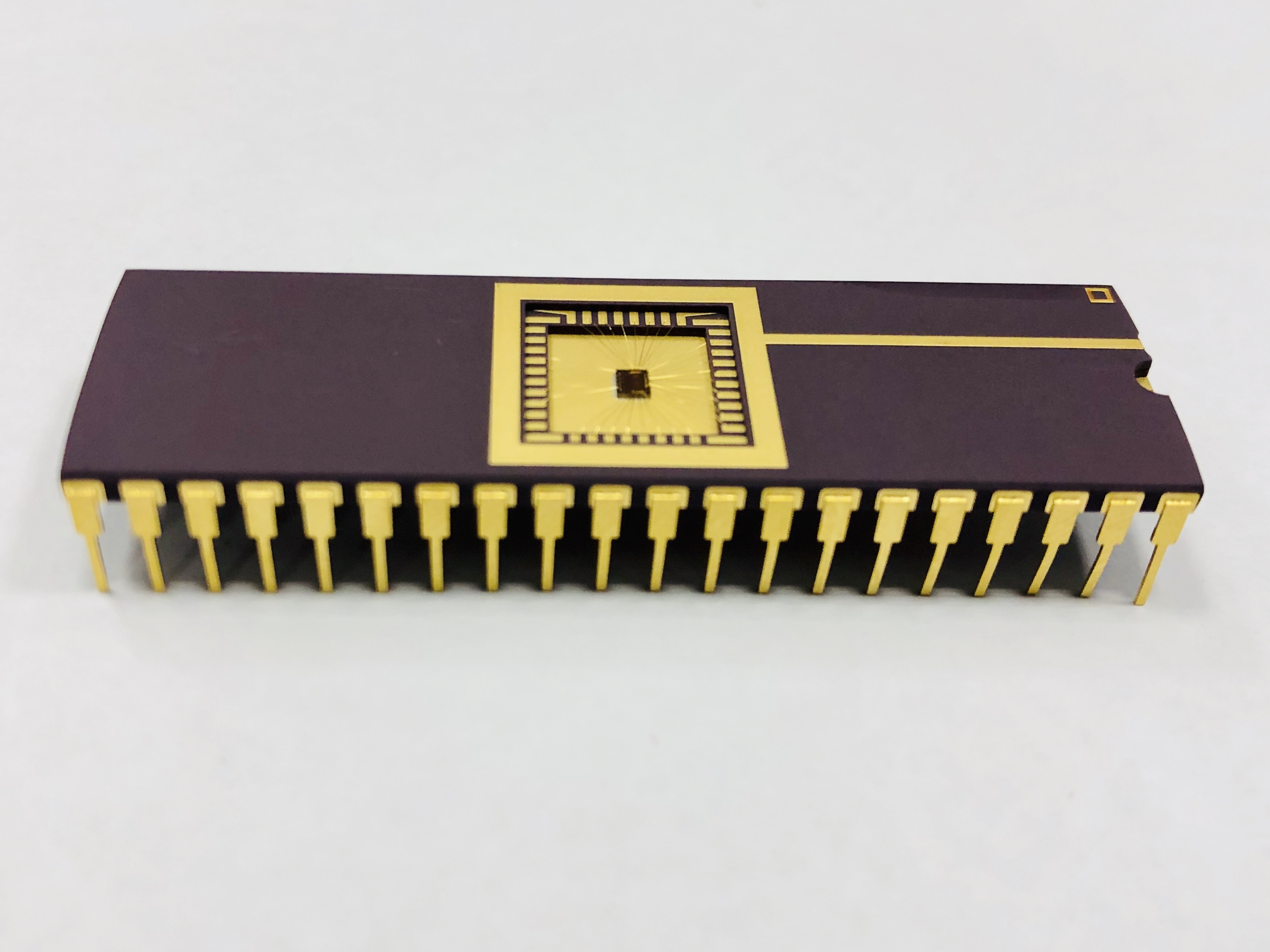

We are a research team in NYU Abu Dhabi, whose main focus is the reliability and security of electronic chips. With the increasing complexity of designs, enhanced capabilities of engraving smaller transistors on silicon, and low-power, high-performance operation requirements, integrated circuits are becoming more and more vulnerable to reliability and security threats. Electronic chips manufactured today exhibit a higher defect rate, fail more often during their mission-mode operation, die quicker in the field, and thanks to globalization and outsourcing, are more prone to security threats such as counterfeiting, IP piracy and hardware trojans.

Our mission is to design these electronic chips with built-in defense mechanisms, in order to expose defective chips more easily and cost-effectively, make them resilient to errors during mission mode, expose any intentional malicious alteration of the chips and protect design IP from reverse engineering. We develop Design-for-Excellence techniques comprising of hardware design blocks and accompanying software CAD tools.

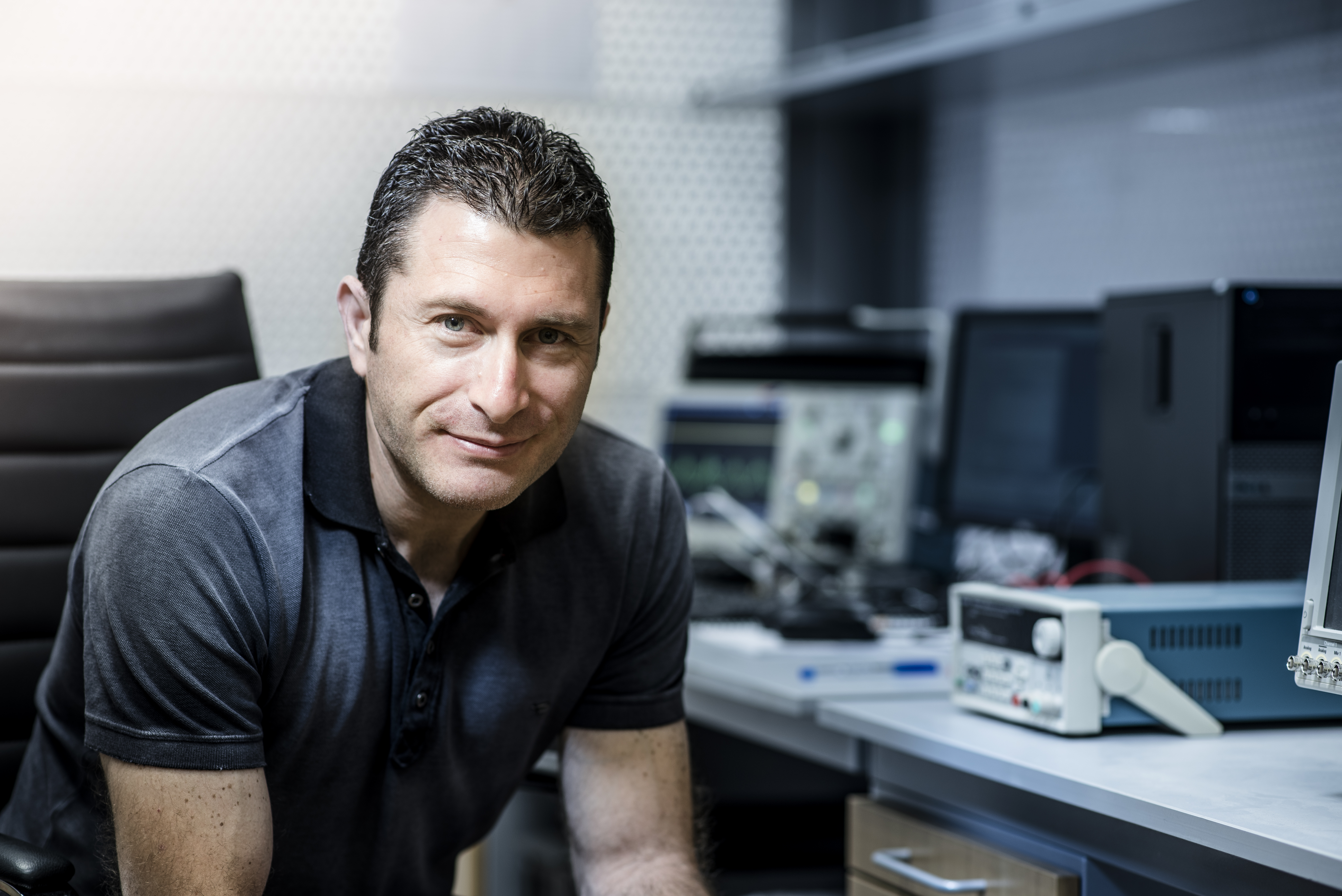

Prof. Ozgur Sinanoglu, Director

The director of the DfX Lab is Prof. Ozgur Sinanoglu, who is a Professor of ECE at New York University in Abu Dhabi. Prof. Ozgur Sinanoglu obtained his Ph.D. in Computer Science and Engineering from University of California, San Diego, in 2004. During his PhD, he was given the IBM PhD Fellowship Award in two consecutive years in 2001 and 2002, and his PhD thesis won the CSE PhD Dissertation Award in UCSD in 2005. Subsequently, he worked for Qualcomm in San Diego as a senior Design-for-Testability engineer, primarily responsible for developing cost-effective test solutions for low-power SOCs. He then joined New York University in Abu Dhabi in 2010. Upon spending his integration year as a visiting Faculty in New York at the ECE Department of NYU Tandon, he joined the Faculty in Abu Dhabi in 2011. His primary field of research is the reliability and security of integrated circuits, mostly focusing on CAD tool development. He has more than 200 conference and journal papers in addition to around 20 issued and pending patents. His research has been funded by US National Science Foundation, US Army Research Office (Department of Defense), DARPA (Department of Defense), Intel Corporation, Semiconductor Research Corporation, GlobalFoundries and Advanced Technology Investment Company.

The director of the DfX Lab is Prof. Ozgur Sinanoglu, who is a Professor of ECE at New York University in Abu Dhabi. Prof. Ozgur Sinanoglu obtained his Ph.D. in Computer Science and Engineering from University of California, San Diego, in 2004. During his PhD, he was given the IBM PhD Fellowship Award in two consecutive years in 2001 and 2002, and his PhD thesis won the CSE PhD Dissertation Award in UCSD in 2005. Subsequently, he worked for Qualcomm in San Diego as a senior Design-for-Testability engineer, primarily responsible for developing cost-effective test solutions for low-power SOCs. He then joined New York University in Abu Dhabi in 2010. Upon spending his integration year as a visiting Faculty in New York at the ECE Department of NYU Tandon, he joined the Faculty in Abu Dhabi in 2011. His primary field of research is the reliability and security of integrated circuits, mostly focusing on CAD tool development. He has more than 200 conference and journal papers in addition to around 20 issued and pending patents. His research has been funded by US National Science Foundation, US Army Research Office (Department of Defense), DARPA (Department of Defense), Intel Corporation, Semiconductor Research Corporation, GlobalFoundries and Advanced Technology Investment Company.

He is currently serving as:

- General Co-chair for IEEE ICCD 2019

- Program Chair for IEEE ICCD 2017

- General Chair for ACM ASIACCS 2017

- Program Co-chair for IEEE ICCD 2016

- Technical Program Committee Member for ITC, DAC, DATE (track chair), VTS, ETS (track chair), VLSI-SOC (track co-chair), ACNS, DFTS, LATS, DTIS

- Journal editorial board member for IEEE TIFS, JETTA, Elsevier MEJ, IET CDT

- Guest Editor for IEEE TCAD (Special Issue on Hardware Security), ACM JETC (Special Issue on Hardware Security), IEEE TETC (Special Issue on Hardware Security), IEEE TETC (Special Issue on Emerging Technologies in Computer Design)

Contact:

- Email: ozgursin at nyu dot edu

- Tel: +971 262 84388

What’s new?

We are looking for PhD candidates to join us.

Current News

DARPA (of US DoD) Award for our Logic Locking Research – Again

DARPA AISS Program funds our research on logic locking. This will be a three year project. We are teaming up with our collaborators from Texas A&M and UT Dallas.

Intel funds our research on secure test interface

Intel funds our three-year project on "Provably-Secure Scan Locking." In this project, we will be working with Intel to develop on-chip defenses to hide plain test and configuration data from third-party (potentially untrustworthy) testers and yet enable them to test...

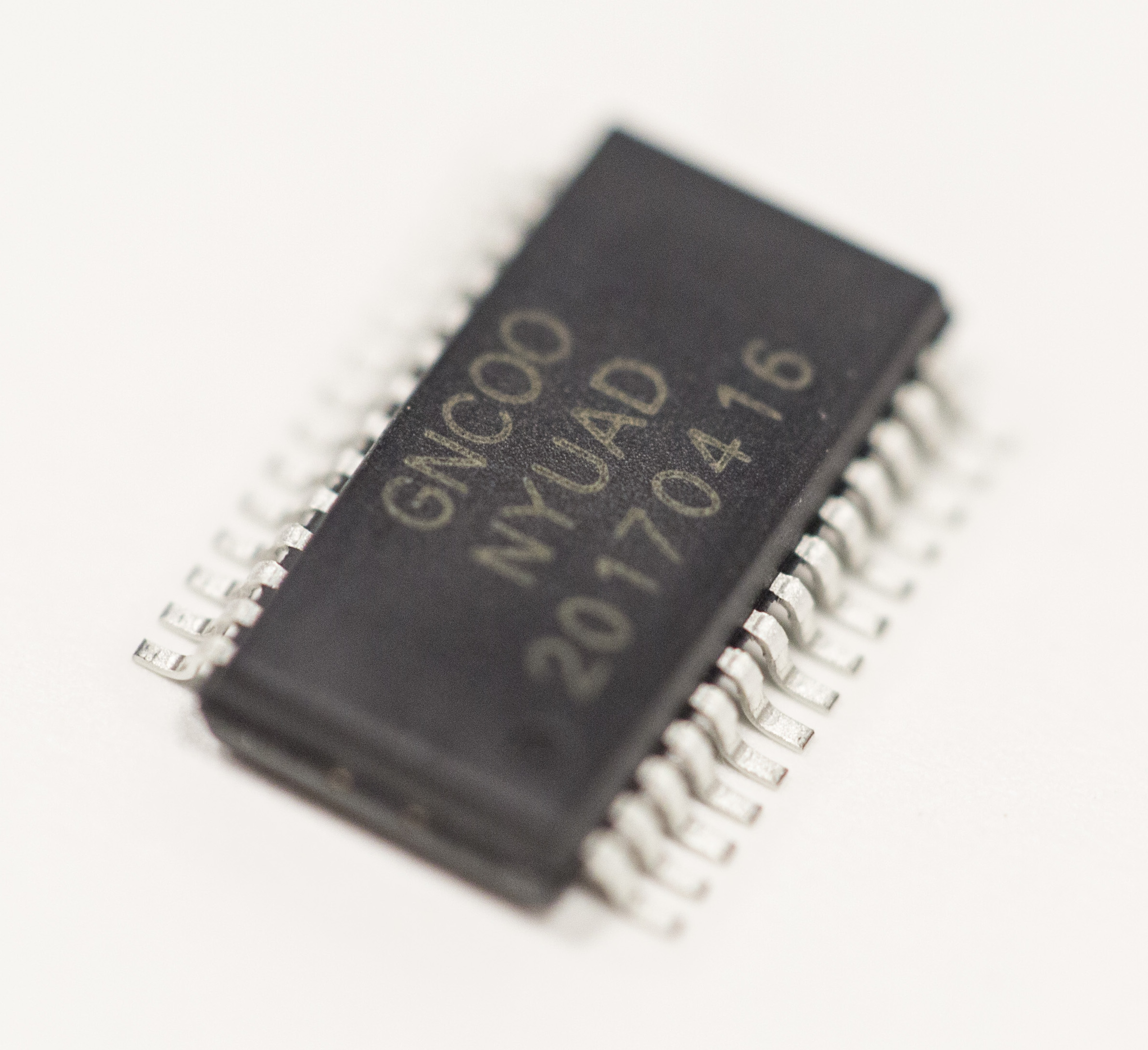

Unhackable chip covered in the National

Our unhackable chip is featured in an article titled “Unhackable Electronic Chip Being Developed in Abu Dhabi” in The National. Click for the National article.

DARPA (of US DoD) Seedling Award for our Logic Locking Research

We won the DARPA seedling grant to further our logic locking research. We are teaming up with UC San Diego, UT Dallas and Texas A&M on this project titled "ECLIPSE: Efficient Cross-Layered IP Protection SchemE." The project duration is 18 months. Seedling grants are...