Implementing SFLL With No Structural Traces

December 2018

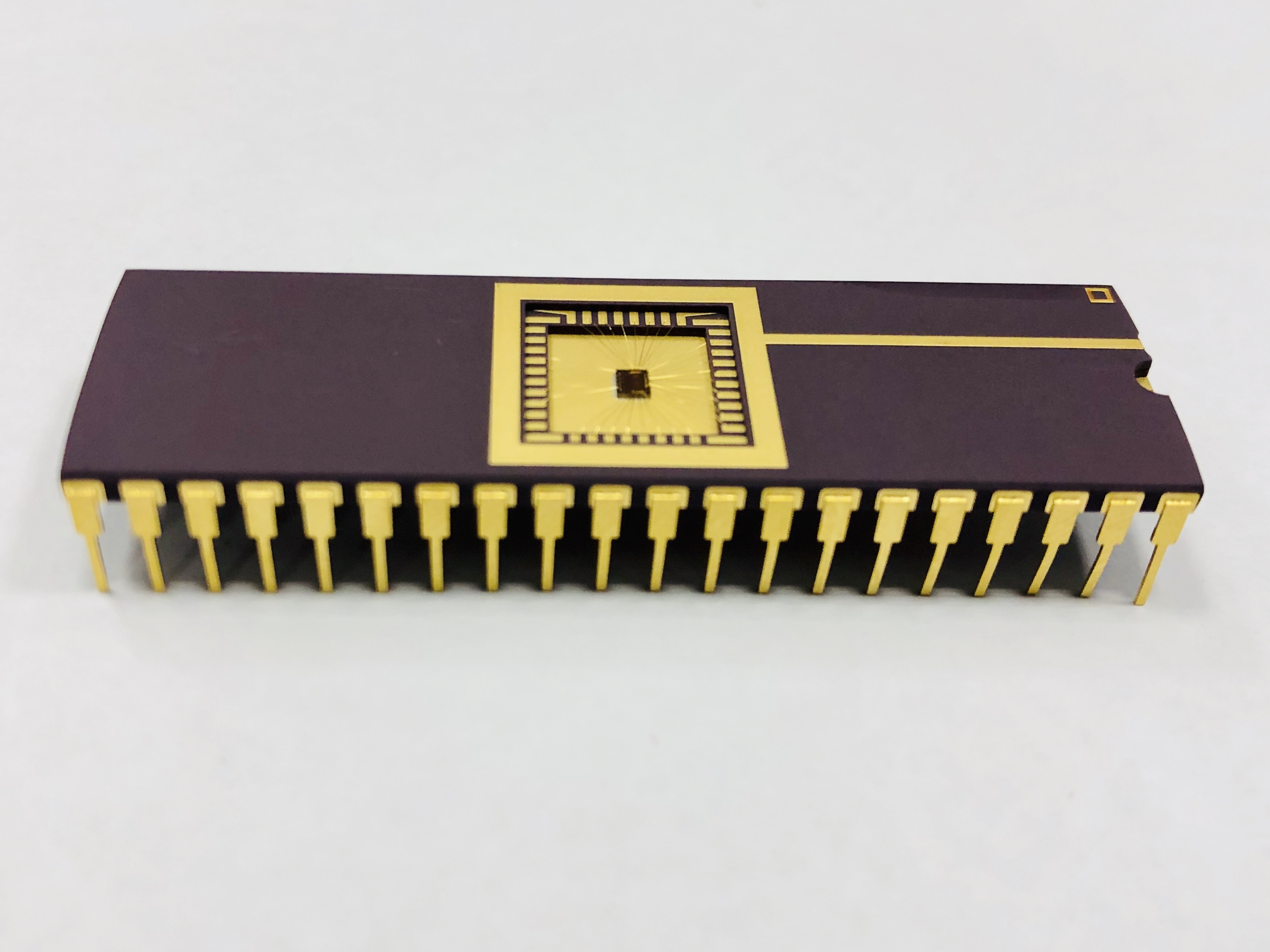

This is the next generation chip that is resilient to untrusted fabrication and reverse engineering. The previous version chip implemented SFLL in a way dependent on the synthesis tools, leaving some structural traces behind, inferring the secret key. In this version, functionality is stripped by truly removing logic; hence, no structural traces are left for the attacker to exploit. All other security guarantees of SFLL are also retained. For more information on this traceless implementation, please refer to the SFLL-fault technique explained in:

“Customized Locking of IP Blocks on a Multi-Million-Gate SoC“, A Sengupta, M Nabeel, A Ashraf, and O Sinanoglu, ICCAD 2018

“ATPG-Based Cost-Effective, Secure Logic Locking“, A Sengupta, M Nabeel, M Yasin, and O Sinanoglu, VTS 2018

Attack Framework: If you think you can identify vulnerabilities in this version, here is a link to access all you need to launch your attack.