Design-for-Testability Techniques

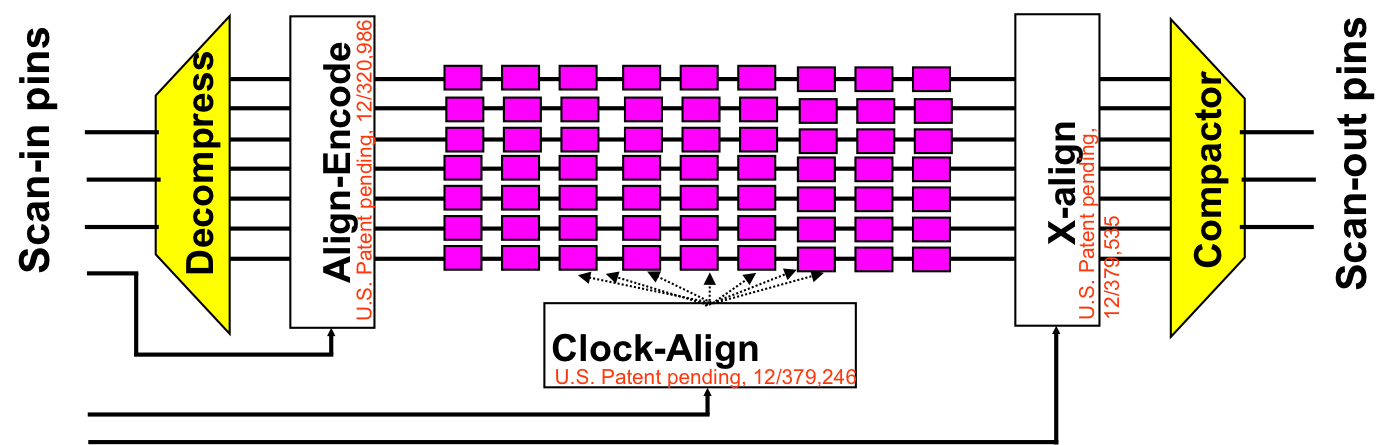

Ever increasing test costs along with time-to-market pressures necessitate aggressive Design-for-Testability (DfT) solutions that are compliant with the existing design flow. We have developed of add-on blocks to be integrated into the conventional compression-based scan architecture, providing DfT engineers ultimate control over Observation of compacted test responses, Controllability of test stimuli through the decompressor, and Dissipation of power during test. We refer to the proposed architecture as the OCD architecture.

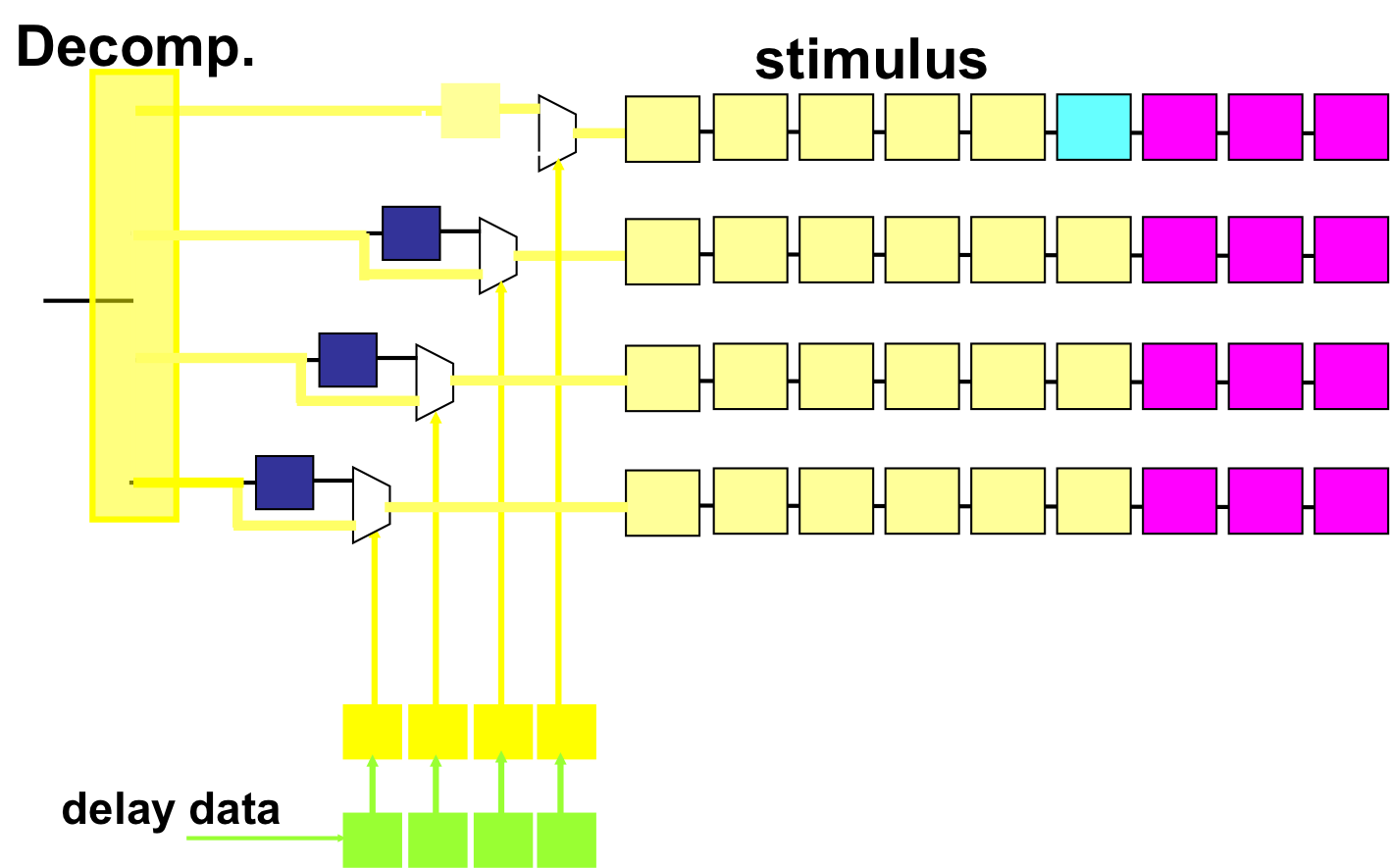

The first additional component, which we refer to as Align-Encode, is to be inserted between the scan input channels and the stimulus decompressor. Align-Encode is controlled directly to manipulate the care bit distribution of a test pattern in such a way that the pattern becomes encodable by the decompressor being utilized in the scan architecture, improving the compression ratio. The exact manipulation of the care bit distribution for a given pattern is determined through algorithms customized with respect to the decompressor. Refer to our papers c28 and j13, or patent p1 for more information.

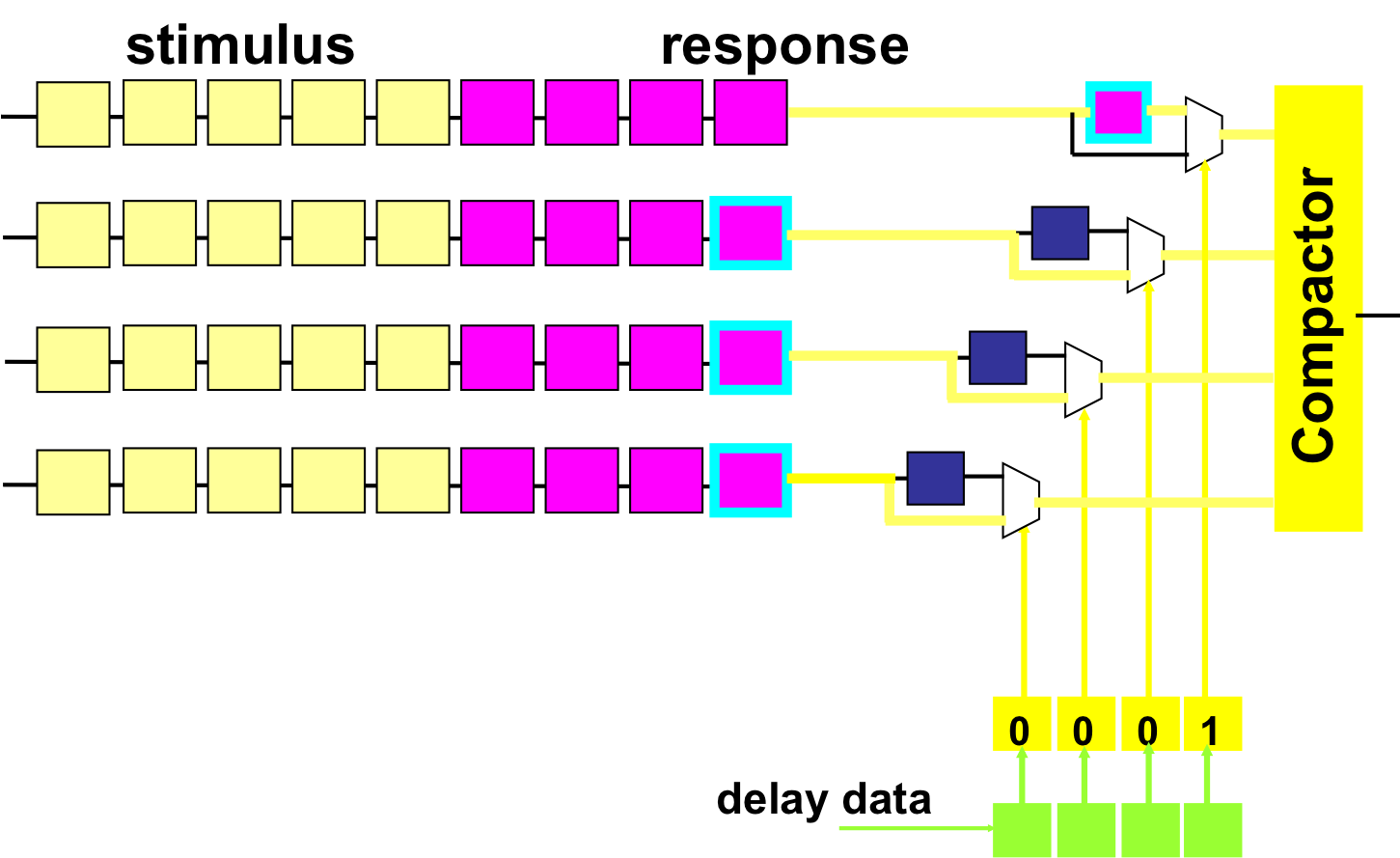

The second additional component in the proposed architecture is X-align, which is to be inserted between the scan chain outputs and the response compactor. X-align is controlled directly to manipulate the distribution of the response x’s with the goal of minimizing the corruption impact of these x’s on the other response bits, improving scan cell observability through the compactor. The manipulation of x distribution has been mapped to the maximum satisfiability problem. Refer to our papers c32, j16 and j28, or patent p3 for more information.

The third additional component in the proposed architecture is the dynamic partition block Clock-Align, which manipulates the scan chain clocks, and thus dynamically partitions scan chains in order to minimize peak power dissipation during test. Refer to our papers c27, j14 and j27, or patent p2 for more information.

The proposed add-on blocks and the associated CAD tools can be seamlessly integrated into the existing design flow, providing a practical yet powerful platform for leashing test costs.

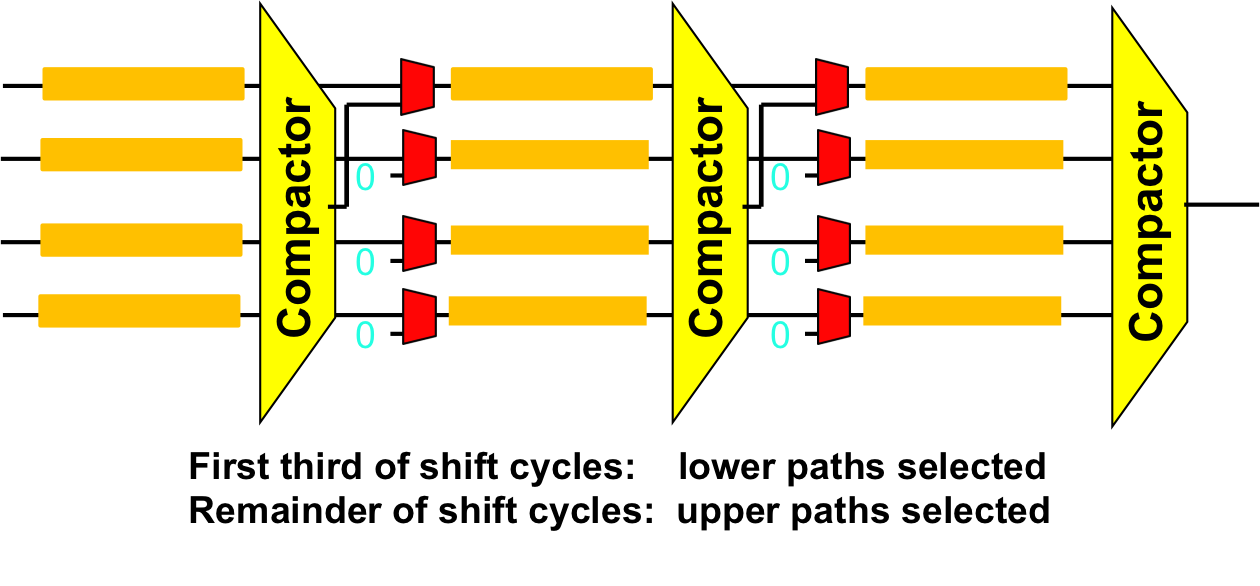

Excessive switching activity during scan operations endangers the reliability of the chip under test. We propose an architectural solution, which we refer to as Expedited-Compact, to mitigate the scan power problem that otherwise creates high heat dissipation and possibly hot spots. Expedited-Compact architecture advances the response compaction operations by utilizing scan chains (the top one in the example) as buffer. This enables the flushing of the transition-wise costly response data out of the system quickly, providing scan-out power savings.In this example, the response compaction operations are completed by the end of the first third of shift cycles; by that time, all the responses in the chains other than the buffer chain are replaced with constant 0’s.

The proposed DfT-based approach is non-intrusive for design flow, requires a very minor investment in area, and in turn delivers significant and predictable savings in test power. The proposed solution reduces average test power without resorting to x-filling, enabling the application of orthogonal x-filling techniques in conjunction.

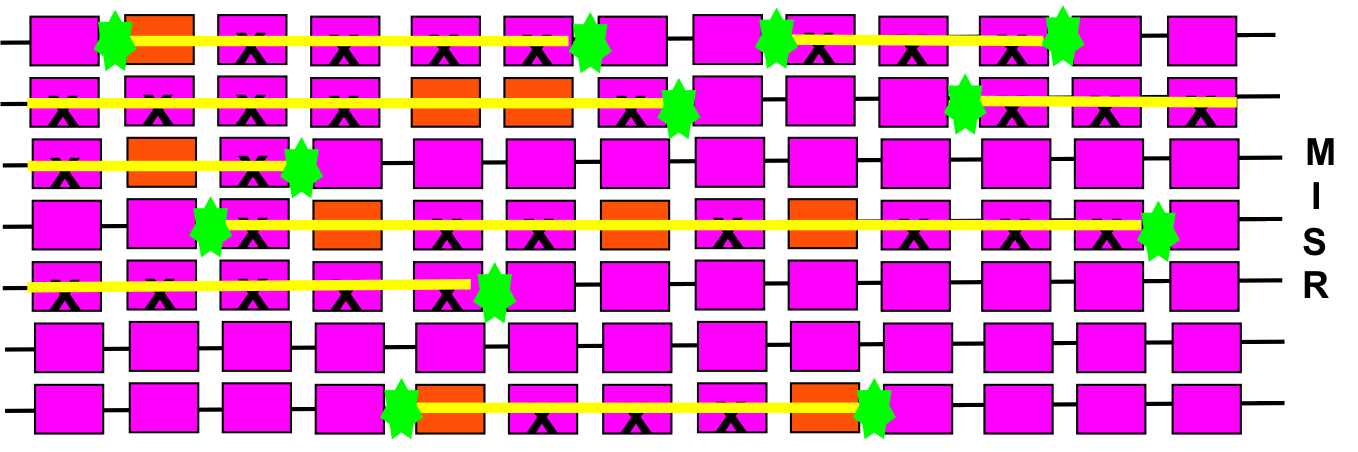

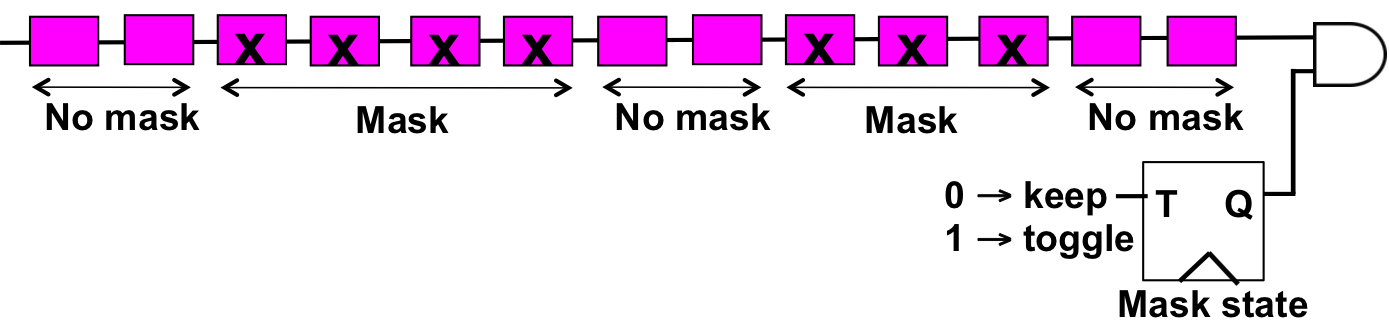

Unknown response bits (x’s) exhibit a clustered distribution in responses due to structural proximity of x sources. We exploited this behavior and developed a toggle-based masking scheme that is capable of delivering very high observability levels in the case of clustered x distributions. Toggle-mask can be used for two purposes. In the first case, all the x’s can be masked along with a minimum number of known response bits (illustrated in the figure). The mask / no-mask decision is toggled in exactly one chain in any shift cycle. A clean MISR signature is produced at the expense of minimal observability (of known response bits) loss. In the second case, toggle-mask can be used as an x-filter that allows a certain number/distribution of x’s to pass, in order to further improve the observability levels. Naturally, the proposed toggle-filter is to be paired with another technique, such as an x-canceling MISR, which is capable of canceling the x’s in the signature via post-processing operations. X-filter can adjust the number/distribution of x in-flow into the MISR, delivering a perfect control over test time and observability. More information can be found in our papers c49 and c61, or patent p8.

Example scan architecture with 7 chains. Toggle-mask eradicates all x’s while losing 9 known response bits.

Masking decisions for one particular chain. Ideal masking; all x’s masked with no loss of any known bits.